CPU基本组成

CPU由 数据通路(data path) 和控制单元(control unit) 两部分组成

data path由算术逻辑单元和寄存器组成 通过数据总线互连

寄存器

- 存储二进制数据的硬件

- 在处理器内部

- 有很多类型

- 写入 & 读取

算术逻辑单元 ALU

Arithmetic Logic Unit

- 执行逻辑运算和算术运算

- 两个输入 一个输出

- 影响状态寄存器

控制单元

监视指令执行和信息传输 取指译码

控制单元根据程序计数器寄存器和状态寄存器中的值 确定执行哪些动作

总线

由数据线 控制线 地址线组成

- 是通信的途径

- 可以连接设备 点对点或者多点总线(公用通道)

- 总线协议 共享总线的规则

- 总线周期:完成总线信息传递所需的时钟间隔

- 每个类型的信息传输在一个总线周期内

- 处理器-内存总线 I/O总线 底板总线

- 我们的个人计算机

- 系统总线连接内部的CPU、内存等内部部件

- 扩展总线(外部总线)连接外部设备 I/O

- 同步总线由时钟控制 设备由时钟频率同步

- 异步总线协调计算机各种操作 采用握手协议

总线仲裁

- 菊花链仲裁方式 daisy chain arbitration优先级高到低 – 不公平

- 集中式并行仲裁方式 centralized parallel arbitration都连通但由中央控制器选择 – 可能会导致瓶颈

- 采用自选择的分配式仲裁方式 distributed arbitration using selfdetection都连通 自身决定优先级和总线使用权

- 采用冲突检测的分配式仲裁方式 (如以太网)distributed arbitration using collision-detection发送请求 冲突则备必须发出另一个请求

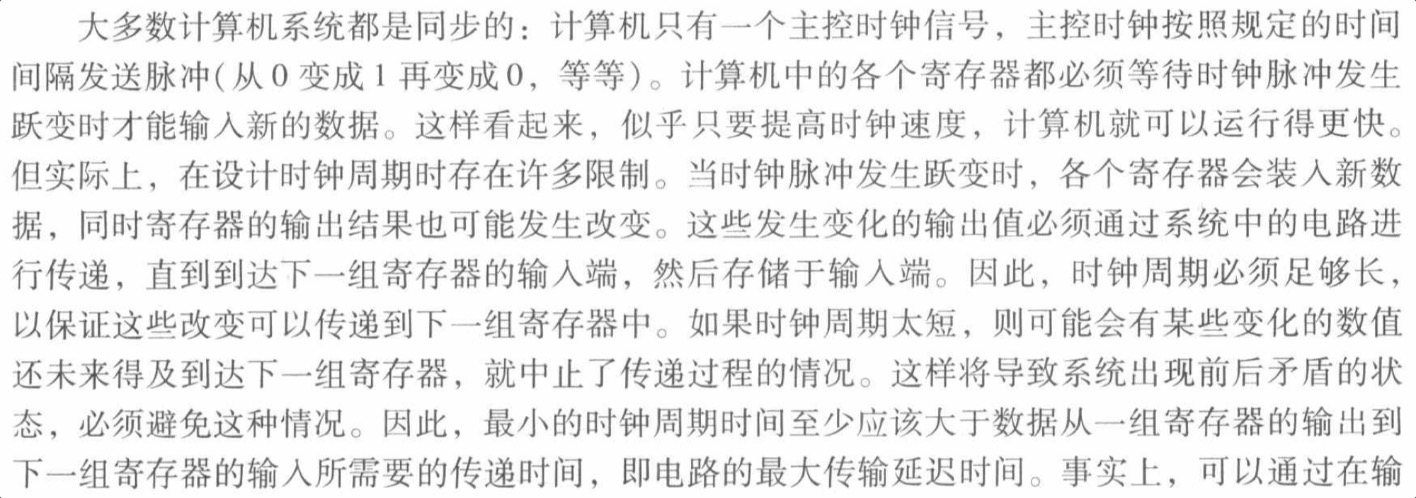

时钟

指令的性能通过时钟周期的数目衡量

时钟频率 = 时钟周期的倒数

时钟频率决定了执行所有操作的速度

总线时钟通常比CPU时钟慢 ⇒ 系统瓶颈:

最小时钟周期要大于最大的延迟(从上一组寄存器开始输出到下一组寄存器的值输入就绪)

执行不同指令需要不同固定的时钟周期

添加寄存器会增加时钟周期

超频:CPU是超频组件 使CPU的时钟频率在总线速度上限之外 从而尽可能降低系统瓶颈 但需要非常小心 可能损坏 或造成时序错误

I/O 子系统

I/O是外围设备和主存储器之间的数据交换

通过I/O设备与计算机进行通信 它们之间采用接口来处理数据交换

数据交换两种方式:

- 存储器映射

- 通过接口中的分配表完成寄存器地址和内存地址的映射

- 提高速度但占空间

- 基于指令

- CPU 有执行输入和输出的专用指令 特定指令

- 不使用内存空间

存储器的组成与寻址方式

RAM 随机存取存储器

- 存储器按字节编址

- 一个字有两个字节 每个单独的字节具有一个唯一的地址

按字节编址 vs. 按字编址

主要区别是地址的单位不同

按字编址是指以“字”为单位来给每个内存单元编上地址。这意味着每个内存单元都会占用一个完整的地址。例如,如果一个字的大小是32位,那么一个内存单元的地址可以是0、4、8、12等。

按字节编址则是以“字节”为单位来给每个内存单元编上地址。这意味着每个内存单元只需要占用一个“字节”大小的地址,而不是一个完整的地址。例如,如果一个字节的大小是8位,那么一个内存单元的地址可以是0、1、2、3等。

按字节编址比按字编址更加灵活,因为它允许内存地址单元的更细粒度控制,但是按字编址会更高效,因为内存的访问是以内存块而不是单个字节进行的,这样可以减少内存访问次数,提高效率。

存储器

- L $\times$ W ⇒ 长x宽(长度x位数)

- 1M = $2^{20}$

- 1K= $2^{10}$

- 2^N 个可寻址存储器单元 ⇒ N 位来唯一寻址每个单元 ⇒ N个地址线

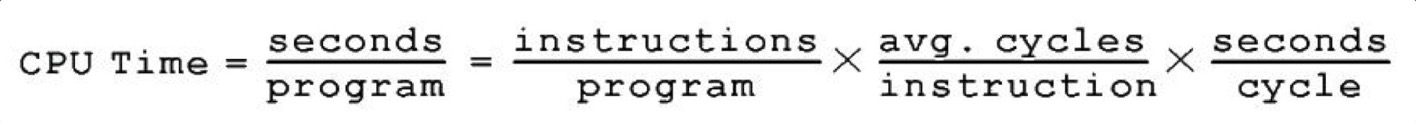

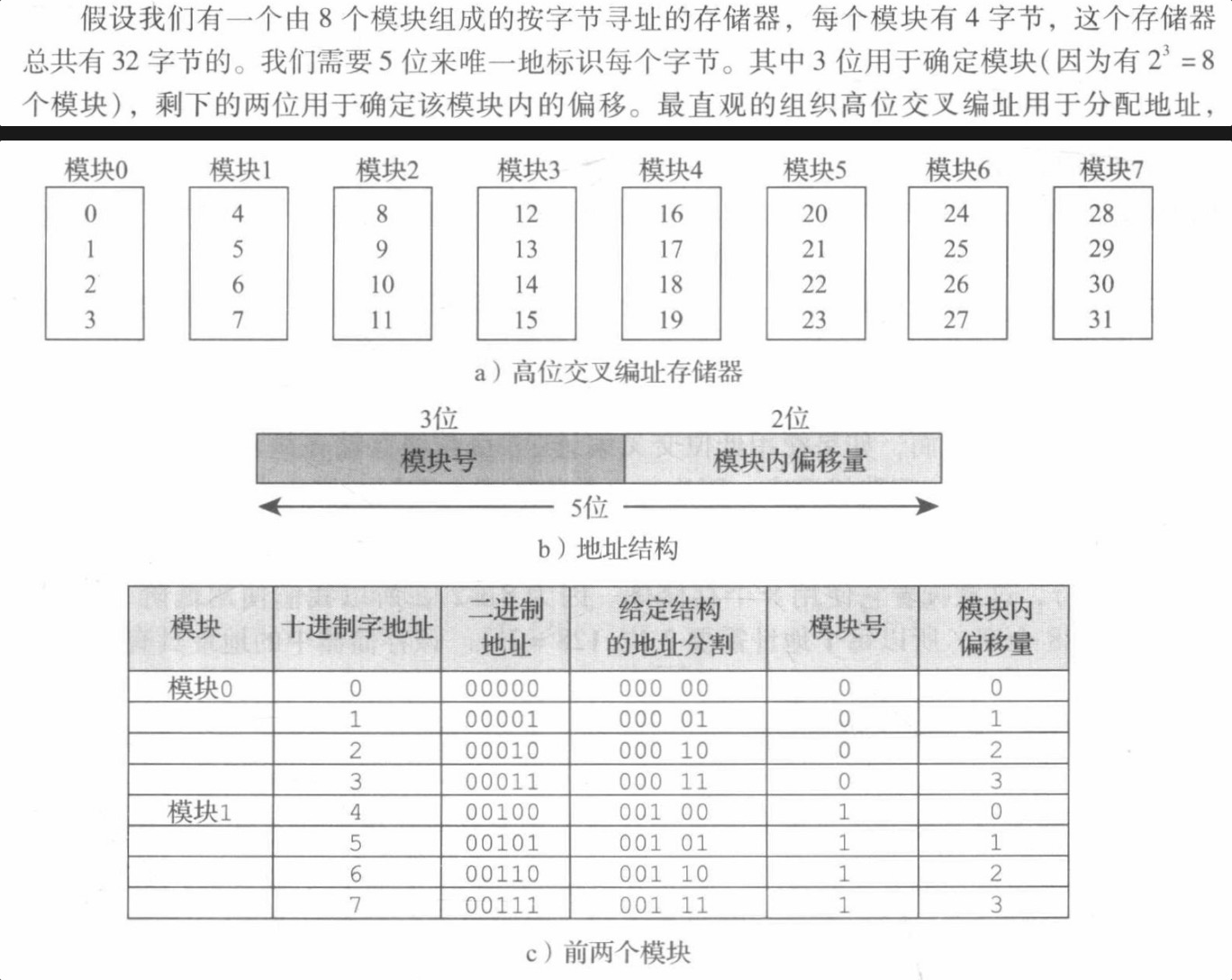

- 单个存储器模块只能串行访问(每次只能执行一次存储器访问) ,而交叉存储器把存储器分成多个存储模块,其中多个模块可以同时访问。

- 模块的数量取决于有多少个可寻址单元,而不是每个可寻址单元的大小。在访问每个模块时将返回一个字,它表示了该架构可寻址单元的长度,如果存储器是 8 路交叉,则可使用8 个模块实现存储器

- 低位交叉时,地址的低位用于选择模块 高位交叉时,地址的高位用于选择模块

示例 (高位交叉):

低位交叉时,3位模块号在右边 总的地址位由总字节数确定 如何分那些位才是由模块数&模块位数确定

- 几路交叉编址 → 几个存储器 = 2^k,k即为模块号的位数

中断

可屏蔽中断 不可屏蔽中断(高优先级中断必须被立刻响应)

可以同步(执行时) 可以异步(意外)

改变程序执行的正常流程

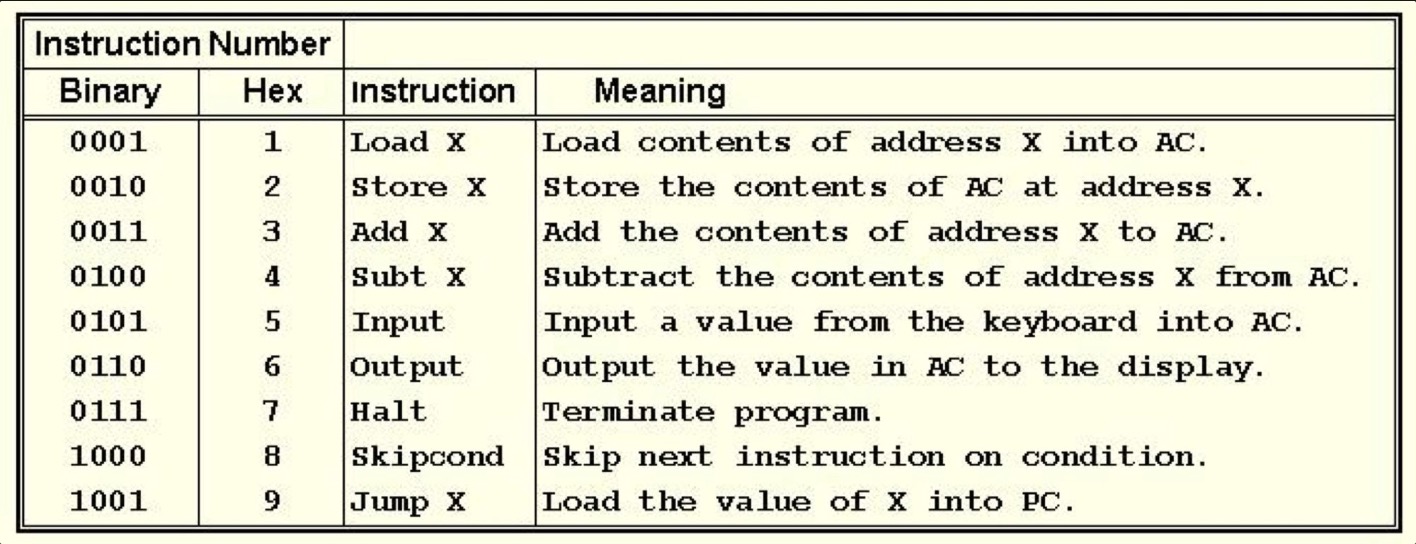

MARIE

按字编址

- 结构

寄存器

- AC – 累加器:是通用寄存器 保存CPU需要处理的数据 16bit

- MAR – 存储器地址寄存器:保存所引用的数据的地址 12bit

- MBR – 存储器缓冲寄存器:保存数据 16bit

- PC – 程序寄存器:保存将要执行的下一条指令的地址 12bit program counter

- IR – 指令寄存器:保存将要执行的下一条指令 16bit

- InREG – 输入寄存器:保存来自输入设备的数据 8bit

- OutREG – 输出寄存器:保存要输出到输出设备的数据 8bit

寄存器之间相互连接 和主存之间经总线(数据总线)连接

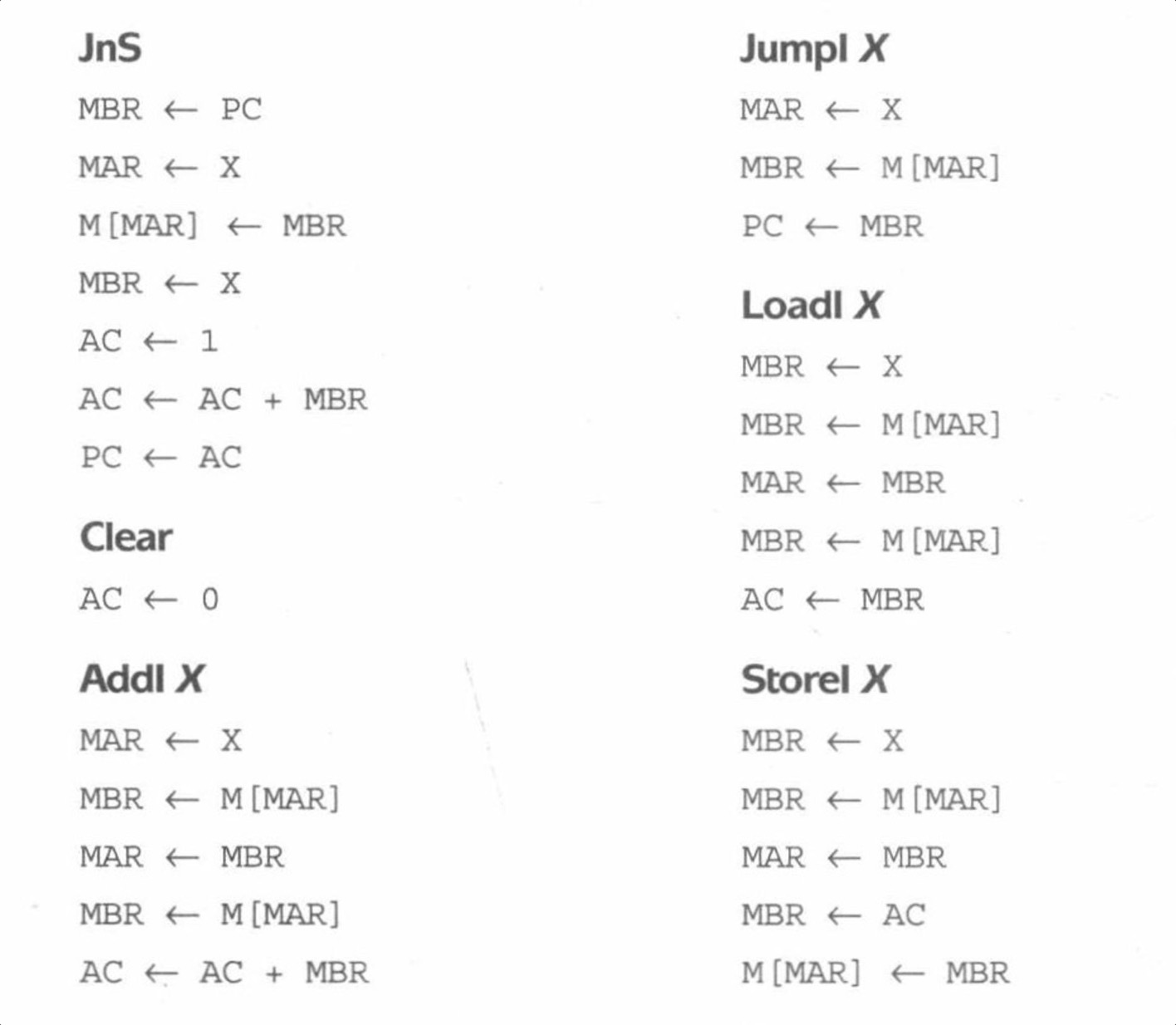

指令集架构&寄存器

寄存器传输语言 register transfer notation (RTN) 寄存器传输表示法 register transfer language(RTL)

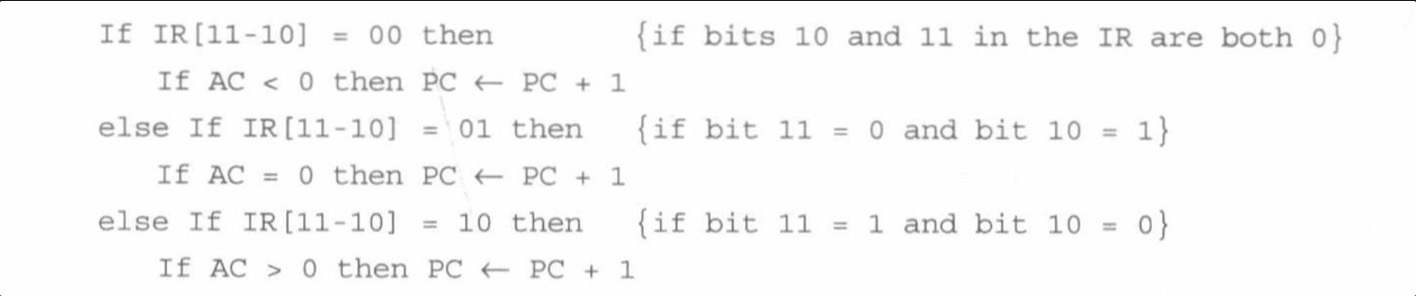

Skipcond:

skipcond 400 ⇒ skipcond 0100 0000 0000 ⇒ if AC=0, skip to next instruction

JnS X:将PC的值存入内存中的X,跳到X+1

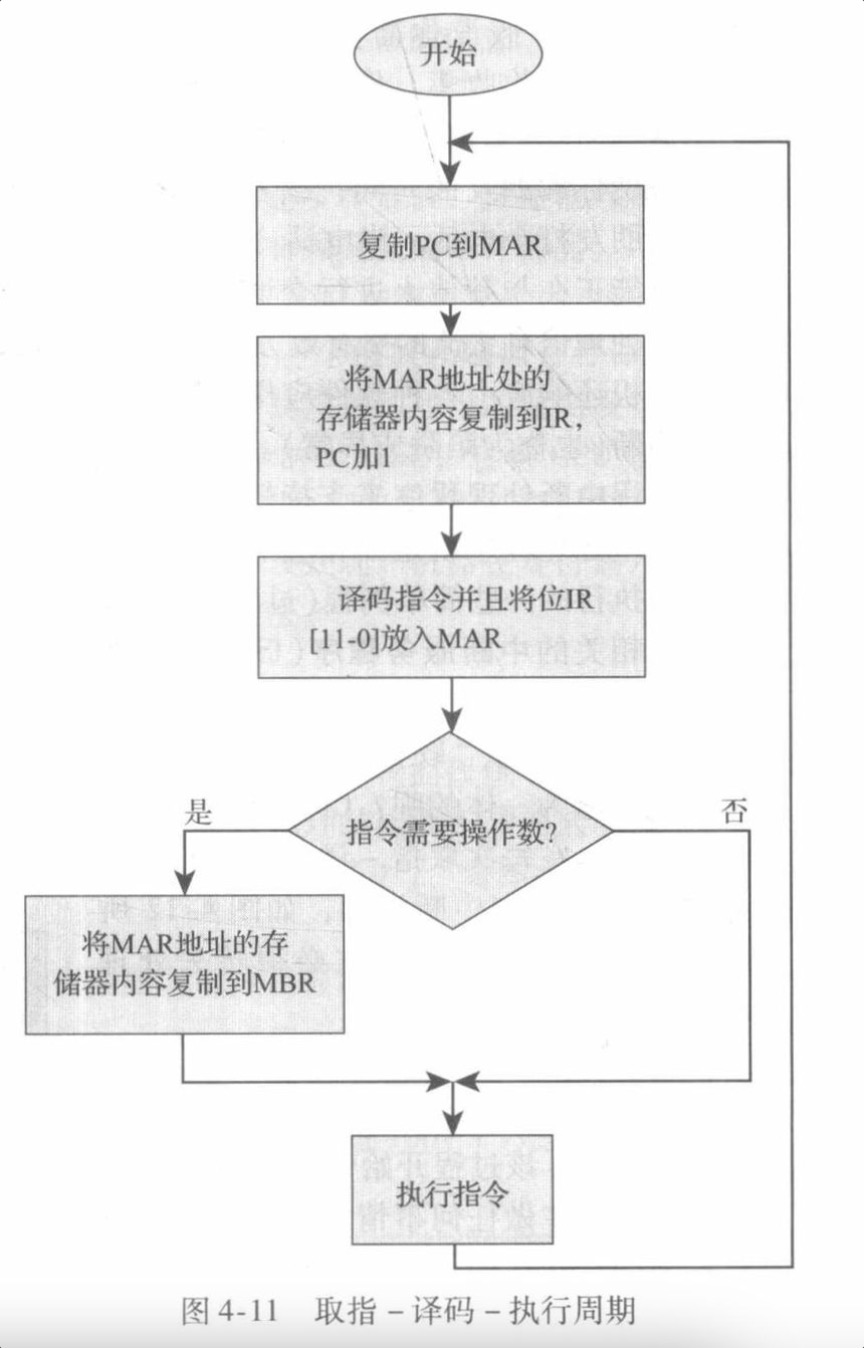

指令执行

PC是12bit 所以复制到MAR,然后再复制到IR的位数一直是12bit,最后IR放回MAR的是低12位

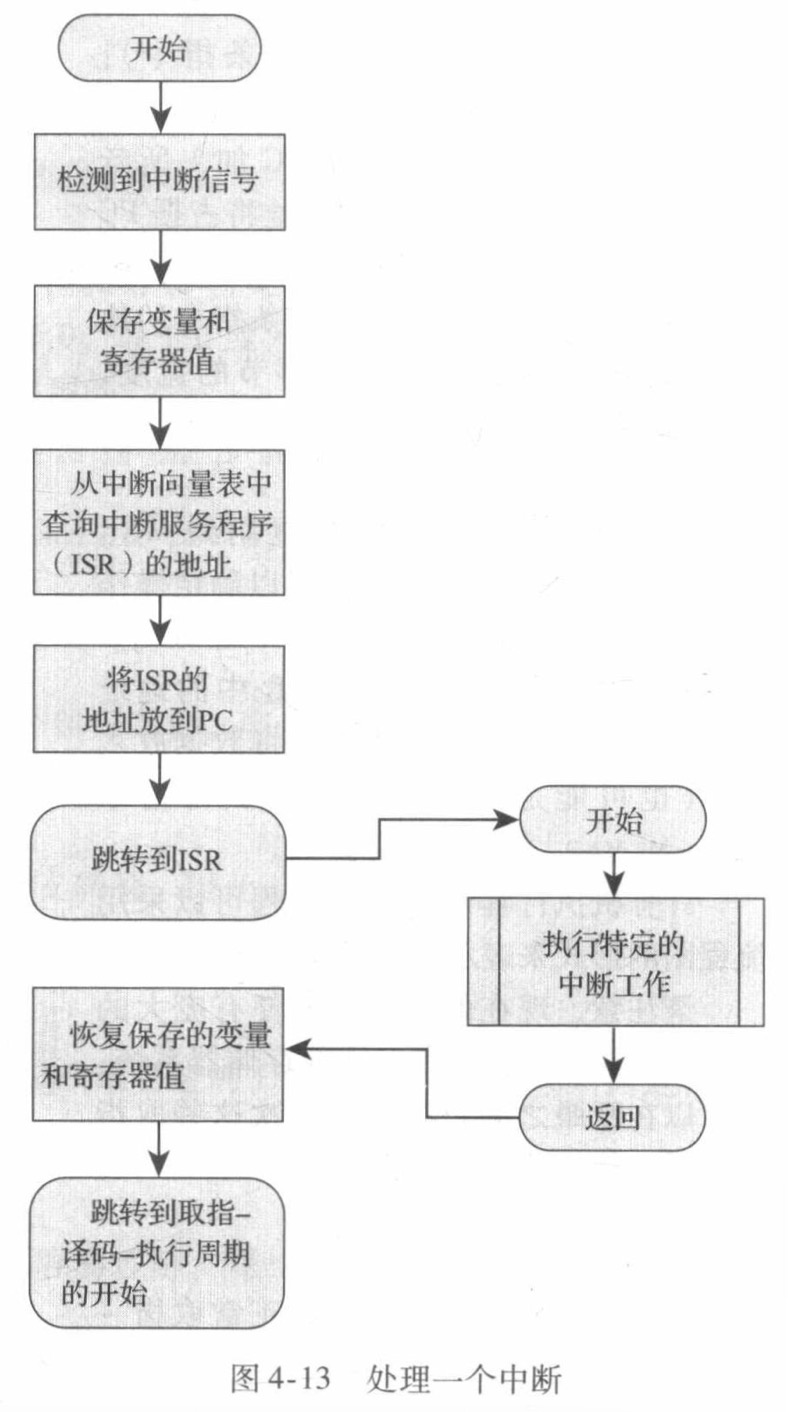

中断可能:

- 各种错误:程序错误 硬件错误

- 用户中断

- I/O请求

在周期执行前先进行中断判断

ISR(Interrupt Service Routine,中断服务程序)

ISR存储在中断向量表中

中断屏蔽:可以通过屏蔽标志寄存器中的关键位来屏蔽可屏蔽中断